Name: \_\_\_\_\_

EEL 4712 Midterm 1 – Spring 2020 VERSION 1

UFID:\_\_\_\_\_

Sign here to give permission to return your test in class, where other students might see your score:

**IMPORTANT:**

• Please be neat and write (or draw) carefully. If we cannot read it with a reasonable effort, it is assumed wrong.

• As always, the best answer gets the most points.

## **COVER SHEET:**

| Problem#:     | Points |            |        |  |

|---------------|--------|------------|--------|--|

| 1 (25 points) |        |            |        |  |

| 2 (12 points) |        |            | Total: |  |

| 3 (15 points) |        |            |        |  |

| 4 (18 points) |        |            |        |  |

| 5 (12 points) |        | Regrade In | fo:    |  |

| 6 (5 points)  |        |            |        |  |

| 7 (4 points)  |        |            |        |  |

| 8 (4 points)  |        |            |        |  |

| 9 (5 points)  | 5      |            |        |  |

|               |        |            |        |  |

|               |        |            |        |  |

|               |        |            |        |  |

|               |        |            |        |  |

```

ENTITY __entity_name IS

PORT( __input_name, __input_name : IN STD_LOGIC;

__input_vector_name : IN STD_LOGIC_VECTOR(__high downto low);

____bidir_name, ___bidir_name : INOUT STD_LOGIC;

___output_name, __output_name : OUT STD_LOGIC);

END entity name;

ARCHITECTURE a OF ___entity_name IS

SIGNAL __signal_name : STD_LOGIC;

BEGIN

-- Process Statement

-- Concurrent Signal Assignment

-- Conditional Signal Assignment

-- Selected Signal Assignment

-- Component Instantiation Statement

END a;

instance name: component name

GENERIC MAP( component generic => connect generic)

PORT MAP ( component port => connect port,

component port => connect port);

WITH __expression SELECT

____signal <= ___expression WHEN ___constant_value,

____expression WHEN ____constant_value,

____expression WHEN ____constant_value;

____signal <= ___expression WHEN __boolean_expression ELSE

_expression WHEN __boolean_expression ELSE

__expression;

IF expression THEN

___statement;

statement;

ELSIF expression THEN

statement;

statement;

ELSE

___statement;

statement;

END IF;

CASE ___expression IS

WHEN constant_value =>

___statement;

statement;

WHEN _____constant_value =>

___statement;

statement;

WHEN OTHERS =>

___statement;

statement;

END CASE;

<generate label>: FOR <loop id> IN <range> GENERATE

-- Concurrent Statement(s)

END GENERATE;

type array_type is array(__upperbound downto __lowerbound);

```

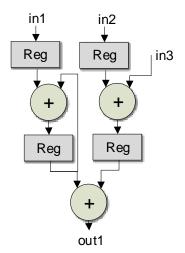

1) (25 points) Fill in the VHDL to implement the illustrated circuit. Assume that clk and rst connect to every register in the schematic. All wires/operations are *width* bits. Ignore adder overflow.

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity example is

generic (width : positive := 8);

port(

clk, rst : in std_logic;

in1, in2, in3 : in std_logic_vector(width-1 downto 0);

out1 : out std_logic_vector(width-1 downto 0));

end example;

architecture BHV of example is

```

begin

```

process(clk, rst)

begin

if (rst = '1') then

```

elsif (rising edge(clk)) then

end if; end process;

end BHV;

2) (12 points) Fill in the VHDL to implement a simple testbench for the specified mux component. The testbench should instantiate a mux using an architecture IF\_STATEMENT. The testbench should test 3 separate input combinations, waiting 10 ns in between tests. The testbench does *not* need to verify the correct output. Declare all signals as std\_logic.

)

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity mux_tb is

end mux_tb;

architecture TB of mux_tb is

begin -- TB

UUT : entity work.mux(

port map (

in1 => in1,

in2 => in2,

sel => sel,

output => output);

process

begin

```

wait; end process; end TB;

- a. (12 points) Identify the violation of the synthesis coding guidelines for *combinational* logic in the following priority encoder code, and state the effect on the synthesized circuit. <u>Note: there are no</u> <u>syntax, casting, or width-mismatch errors.</u>

- b. (3 points) Fix the violation with a single line of code.

```

library ieee;

use ieee.std logic 1164.all;

entity pe is

port (

input : in std logic vector(3 downto 0);

output : out std_logic_vector(1 downto 0);

valid : out std_logic

);

end pe;

architecture default of pe is

begin

process(input)

begin

if (input(3) = '1') then

output <= "11";</pre>

elsif (input(2) = '1') then

output <= "10";</pre>

elsif (input(1) = '1') then

output <= "01";</pre>

elsif (input(0) = '1') then

output <= "00";

else

output <= "00";</pre>

valid <= '0';</pre>

end if;

end process;

```

end default;

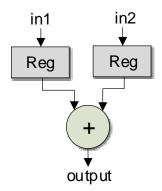

4) (18 points) Fill in the provided code to create the illustrated circuit as a structural architecture using the specified reg and add components. Connect each reg to the clock and reset (not shown in figure). All reg and add instances should use the *width* of the *structure* entity. Use the next page if necessary.

```

library ieee;

use ieee.std_logic_1164.all;

entity structure is

generic (width : positive := 16);

: in std_logic;

: in std_logic;

port (clk

rst

in1, in2 : in std logic vector(width-1 downto 0);

output : out std_logic_vector(width-1 downto 0));

end structure;

architecture STR of structure is

component reg

generic (width : positive := 8);

port (clk, rst : in std logic;

input : in std_logic_vector(width-1 downto 0);

output : out std_logic_vector(width-1 downto 0));

end component;

component add

generic (width : positive := 8);

port (in1, in2 : in std logic vector(width-1 downto 0);

output : out std_logic_vector(width-1 downto 0));

end component;

```

begin

## 5) (12 points)

a. (3 points) Resources grow \_\_\_\_\_ with width for a carry lookahead adder.

- b. (3 points) **True/false**. Due to fan-in limitations, carry lookahead adders tend to have a latency that increases quadratically with width.

- c. (3 points) **True/false**. A ripple-carry adder using blocks of carry-lookahead adders instead of full adders has a delay that increases logarithmically with width.

- d. (3 points) Define the logic for the carry out c4 of a carry look-ahead adder (CLA) in terms of the propagate signals (p<sub>i</sub>), generate signals (g<sub>i</sub>), and carry in (c<sub>0</sub>).

- 6) (5 points) For the following process, what will the values of x and y be at the <u>end of the process</u> when x= 20, y = 30, and the process is triggered by in1 becoming 50? Explain your answer for partial credit.

- 7) (4 points) **True/false**. A single assignment to all outputs at the beginning of a process for combinational logic will guarantee there are no latches for that logic.

- 8) (4 points) **True/false**. Multiple concurrent assignments to a signal are not synthesizable, but it is valid to assign the same signal sequentially inside a process and concurrently outside a process.

- 9) 5 free points for having to take a test at 8:30am.