| EEL 4712  | Name:                                                                                       |

|-----------|---------------------------------------------------------------------------------------------|

| Midterm   | 1 – Spring 2019                                                                             |

| VERSION   | , -                                                                                         |

|           | UFID:                                                                                       |

|           |                                                                                             |

| Sign here | to give permission to return your test in class, where other students might see your score: |

|           |                                                                                             |

|           |                                                                                             |

|           |                                                                                             |

| _         |                                                                                             |

|           | IMPORTANT:                                                                                  |

|           | Please be neat and write (or draw) carefully. If we cannot read it with a                   |

|           | reasonable effort, it is assumed wrong.                                                     |

• As always, the best answer gets the most points.

## **COVER SHEET:**

| Problem#:     | Points |

|---------------|--------|

| 1 (25 points) |        |

| 2 (9 points)  |        |

| 3 (14 points) |        |

| 4 (15 points) |        |

| 5 (5 points)  |        |

| 6 (5 points)  |        |

| 7 (5 points)  |        |

| 8 (5 points)  |        |

| 9 (12 points) |        |

| 10 (5 points) | 5      |

| Total: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

| Regrade Info | • |  |  |

|--------------|---|--|--|

|              |   |  |  |

|              |   |  |  |

|              |   |  |  |

|              |   |  |  |

|              |   |  |  |

|              |   |  |  |

|              |   |  |  |

|              |   |  |  |

|              |   |  |  |

|              |   |  |  |

|              |   |  |  |

|              |   |  |  |

```

ENTITY _entity_name IS

PORT(__input_name, __input_name : IN STD_LOGIC;

__input_vector_name : IN STD_LOGIC_VECTOR(__high downto __low);

bidir_name, __bidir_name : INOUT STD_LOGIC;

output_name, __output_name : OUT STD_LOGIC);

END entity name;

ARCHITECTURE a OF entity name IS

SIGNAL __signal_name : STD_LOGIC;

BEGIN

-- Process Statement

-- Concurrent Signal Assignment

-- Conditional Signal Assignment

-- Selected Signal Assignment

-- Component Instantiation Statement

END a;

instance_name: __component_name

GENERIC MAP ( component generic => connect generic)

PORT MAP (__component_port => __connect_port,

__component_port => __connect_port);

WITH expression SELECT

__signal <= __expression WHEN __constant_value,

__expression WHEN __constant_value,

__expression WHEN __constant_value, __expression WHEN __constant_value;

__signal <= __expression WHEN __boolean_expression ELSE

__expression WHEN __boolean_expression ELSE

__expression;

IF expression THEN

statement;

statement;

ELSIF expression THEN

__statement;

statement;

ELSE

__statement;

statement;

END IF;

CASE __expression IS

__constant_value =>

WHEN

__statement;

statement;

WHEN constant value =>

__statement;

statement;

WHEN OTHERS =>

__statement;

statement;

END CASE;

<generate_label>: FOR <loop_id> IN <range> GENERATE

-- Concurrent Statement(s)

END GENERATE;

type array type is array( upperbound downto lowerbound);

```

1) (25 points) Fill in the VHDL to implement the illustrated circuit. Assume that clk and rst connect to every register in the schematic. All wires/operations are *width* bits except for in4, which is a single bit. Ignore adder overflow. Assume the mux selects the left input when the select = '1'. Use the next page if necessary.

```

in1 in2

in3

in4

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric_std.all;

entity example is

generic (width : positive := 8);

port(

clk, rst

: in std_logic;

Reg

Reg

Reg

in1, in2, in3 : in std_logic_vector(width-1 downto 0);

in4 : in std_logic;

\downarrow

: out std_logic_vector(width-1 downto 0));

out1

2x1

end example;

architecture BHV of example is

out1

```

```

begin

process(clk, rst)

begin

if (rst = '1') then

```

```

elsif (rising_edge(clk)) then

```

```

end if;

end process;

```

- 2) (9 points) Given the two following entities alu and alu top:

- a. (3 points) Modify the generic map for alu instantiation in *alu\_top* to create an alu with a width of 7 bits.

- b. (3 points) Assume that entity *alu* has 2 architectures: FAST and SMALL. Modify the alu instantiation in *alu\_top* to explicitly use the FAST architecture.

- c. (3 points) True/False. The initialization of width to 4 in the *alu* entity's generic definition overrides any value specified in the generic map.

```

entity alu is

generic (

width : positive := 4);

port (

: in std logic vector(width-1 downto 0);

in1

in2 : in std_logic_vector(width-1 downto 0);

sel : in std_logic_vector(1 downto 0);

output : out std_logic_vector(width-1 downto 0));

end alu;

library ieee;

use ieee.std logic 1164.all;

entity alu top is

port (

in1

: in std logic vector(6 downto 0);

in2 : in std_logic_vector(6 downto 0);

sel : in std_logic_vector(1 downto 0);

output : out std_logic_vector(6 downto 0));

end alu top;

architecture STR of alu top is

begin

U_ALU : entity work.alu

generic map (

port map (

in1 => in1,

in2 => in2,

sel => sel,

```

output => output);

end STR;

- 3) a. (10 points) Identify the violation of the synthesis coding guidelines for *combinational* logic in the following code, and state the effect on the synthesized circuit. Note: there are no syntax, casting, or width-mismatch errors.

- b. (4 points) Fix the violation with a single line of code.

```

process(en, state)

begin

case state is

when STATE 0 =>

output <= "0001";

if (en = '1') then

next_state <= STATE_1;</pre>

end if;

when STATE 1 =>

output <= "0010";

if (en = '1') then

next_state <= STATE_2;</pre>

end if;

when STATE 2 =>

output <= "0100";

if (en = '1') then

next_state <= STATE_3;</pre>

end if;

when STATE_3 =>

output <= "1000";

if (en = '1') then

next_state <= STATE_0;</pre>

end if;

when others => null;

end case;

end process;

```

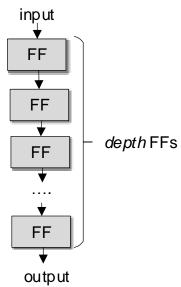

4) (15 points) Fill in the provided code to create the illustrated circuit as a structural architecture using the specified FF component. Connect each FF to the clock and reset (not shown in figure). Use the next page if necessary.

begin

| 5)      | (5 points) Create a for loop that defines the generate (g) and propagate (p) bits for a CLA in terms of inputs x and y. Assume that g, p, x, and y are all std_logic_vector signals of width bits. Note: you do not need the carry logic, just the generate and propagate.                                                                                                                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | process(x, y) begin                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | end process;                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6)      | <ul> <li>(5 points) When is it safe to use a for loop in synthesizable code (choose the best answer):</li> <li>a. When feedback from one register to another is required in the circuit</li> <li>b. When you need to chain multiple operations into a single cycle</li> <li>c. When the unrolled version of the loop corresponds to the intended circuit</li> <li>d. When the number of iterations of the loop is known at compile time</li> </ul> |

| 7)      | (5 points) Explain why the following code will have errors during compilation/synthesis (assume the numeric_std package is used):                                                                                                                                                                                                                                                                                                                  |

| sig     | nal x, y, z : std_logic_vector(7 downto 0);                                                                                                                                                                                                                                                                                                                                                                                                        |

| <br>X < | = unsigned(y) + unsigned(z);                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8)      | (5 points) Explain why the following code will have errors during compilation/synthesis (assume the numeric_std package is used):                                                                                                                                                                                                                                                                                                                  |

| _       | nal in1, in2 : unsigned(7 downto 0);<br>nal sum : unsigned(8 downto 0);                                                                                                                                                                                                                                                                                                                                                                            |

| sui     | m <= in1 + in2;                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9)  | (12 poi  | nts)                                                                                                                                                                                                     |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | a.       | (2 points) What type of relationship exists between area/resources and width for a ripple-carry adder?                                                                                                   |

|     | b.       | (2 points) Why in practice does a carry-lookahead adder not actually achieve a constant propagation delay?                                                                                               |

|     | C.       | (2 points) True/false. A 2-level carry-lookahead adder uses fewer resources as width increases than a single level, without an increase in delay.                                                        |

|     | d.       | (2 points) For the hierarchical carry-lookahead adder, how much does the width have to increase for the propagation delay to increase?                                                                   |

|     | e.       | (2 points) <b>True/false</b> . The delay of a ripple-carry adder using blocks of carry-lookahead adders, instead of full adders, achieves a constant propagation delay when ignoring fan-in limitations. |

|     | f.       | (2 points) Define the logic for the carry out c4 of a carry look-ahead adder (CLA) in terms of the propagate signals ( $p_i$ ), generate signals ( $g_i$ ), and carry in ( $c_0$ ).                      |

| 10) | 5 free p | points for having to take a test at 8:30am.                                                                                                                                                              |