| EEL 4712<br>Midterm 2 – Spring 2                                             | 2014                                                       | Name: |                                           |  |  |  |  |  |

|------------------------------------------------------------------------------|------------------------------------------------------------|-------|-------------------------------------------|--|--|--|--|--|

| VERSION 1                                                                    |                                                            | UFID: |                                           |  |  |  |  |  |

| Sign your name here if you would like for your test to be returned in class: |                                                            |       |                                           |  |  |  |  |  |

|                                                                              |                                                            |       |                                           |  |  |  |  |  |

| reasonab                                                                     | be neat and wri<br>ble effort, it is as<br>ays, the best a |       | y. If we cannot read it with a st points. |  |  |  |  |  |

| Problem#:                                                                    | Points                                                     |       |                                           |  |  |  |  |  |

| 1 (10 points)                                                                |                                                            |       | Total:                                    |  |  |  |  |  |

| 2 (6 points)                                                                 |                                                            |       | Total.                                    |  |  |  |  |  |

| 3a (6 points)                                                                |                                                            |       |                                           |  |  |  |  |  |

| 3b (6 points)                                                                |                                                            |       |                                           |  |  |  |  |  |

| 4 (18 points)                                                                |                                                            |       |                                           |  |  |  |  |  |

| 5a (20 points)                                                               |                                                            |       |                                           |  |  |  |  |  |

| 5b (15 points)                                                               |                                                            |       |                                           |  |  |  |  |  |

| 5c (15 points)                                                               |                                                            |       |                                           |  |  |  |  |  |

| 6 (4 points)                                                                 | 4                                                          |       |                                           |  |  |  |  |  |

| Regrade Info:                                                                |                                                            |       |                                           |  |  |  |  |  |

|                                                                              |                                                            |       |                                           |  |  |  |  |  |

|                                                                              |                                                            |       |                                           |  |  |  |  |  |

|                                                                              |                                                            |       |                                           |  |  |  |  |  |

|                                                                              |                                                            |       |                                           |  |  |  |  |  |

|                                                                              |                                                            |       |                                           |  |  |  |  |  |

```

ENTITY _entity_name IS

PORT( input name, input name: IN STD LOGIC;

input vector name: IN STD LOGIC VECTOR( high downto low);

_bidir_name, __bidir_name : INOUT STD_LOGIC;

output name, output name: OUT STD LOGIC);

END entity name;

ARCHITECTURE a OF entity name IS

SIGNAL __signal_name : STD_LOGIC;

BEGIN

-- Process Statement

-- Concurrent Signal Assignment

-- Conditional Signal Assignment

-- Selected Signal Assignment

-- Component Instantiation Statement

END a;

__instance_name: __component_name PORT MAP (__component_port => __connect_port,

component port => connect port);

WITH expression SELECT

_signal <= __expression WHEN __constant_value,

expression WHEN __constant_value,

_expression WHEN __constant_value,

_expression WHEN __constant_value;

signal <= __expression WHEN __boolean_expression ELSE

expression WHEN __boolean_expression ELSE

expression;

IF expression THEN

statement;

statement;

ELSIF expression THEN

_statement;

statement;

ELSE

__statement;

statement:

END IF;

CASE __expression IS

WHEN __constant_value =>

statement;

statement;

WHEN __constant_value =>

statement;

statement;

WHEN OTHERS =>

statement;

statement;

END CASE;

<generate label>: FOR <loop id> IN <range> GENERATE

-- Concurrent Statement(s)

END GENERATE;

type __identifier is type_definition;

subtype identifier is subtype indication;

```

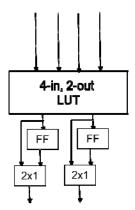

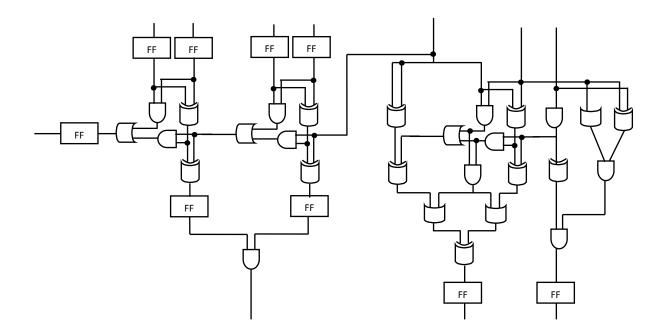

1) (10 points) Assume you are given an FPGA that consists of the following CLB structures:

Map the following circuit onto these CLBs by drawing rectangles to represent CLBs. Use the minimum number of CLBs.

| (6 points) Connection boxes and switch boxes are used for which of the following (only choose one):                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>(a) Configuring the internals of a DSP unit to perform different operations</li> <li>(b) Connecting LUTs within CLBs (e.g., carry chains)</li> <li>(c) Providing reconfigurable interconnect between CLBs, DSPs, block RAMs, and I/O</li> <li>(d) Implementing addressing logic for distributed RAM components</li> <li>(e) Distributing clock signals without timing problems</li> </ul> |

| a. (6 points) For a 25 MHz clock, what is the range of a counter (i.e., the number of cycles to count) that determines when 100 ms have elapsed?                                                                                                                                                                                                                                                   |

| b. (6 points) You are designing a circuit with a 50 MHz input clock that generates an output clock pulse when an asynchronous control input (e.g., a button) has been asserted for 1 second. However, it is not possible to guarantee that the input has been asserted for exactly 1 second. <b>Briefly</b> explain why and show the minimum range of absolute error.                              |

|                                                                                                                                                                                                                                                                                                                                                                                                    |

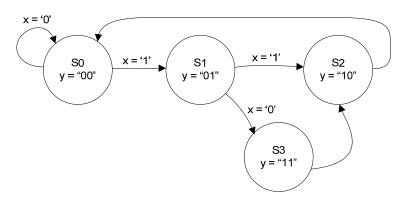

4) (18 points) Fill in the code to implement the following Moore finite state machine (FSM), using the 2-process FSM model. Assume that if an edge does not have a corresponding condition, that edge is always taken on a rising clock edge. Assume that S0 is the start state. Use the next page if extra room is needed.

```

library ieee;

use ieee.std_logic_1164.all;

entity fsm is

port (

clk, rst, x : in std logic;

: out std_logic_vector(1 downto 0));

У

end fsm;

architecture PROC2 of fsm is

type STATE_TYPE is (S0, S1, S2, S3);

signal state, next_state : STATE_TYPE;

begin

process(clk, rst)

begin

if (rst = '1') then

elsif (clk'event and clk = '1') then

end if;

end process;

process(

begin

```

5) a. (20 points) Create an FSMD that implements the following pseudo-code. **Do not write VHDL** and instead leave the FSMD in graphical form (i.e., state machine with corresponding operations in each state). Make sure to specify all operations and state transitions. Note that output, go, num, dem, and done are I/O.

```

Inputs: go, num, den

Outputs: output, done

int i;

// reset values for outputs

done = 0; output = 0;

while (1) {

while (go == 0);

done = 0;

i = 0;

// Store inputs in a register

num reg = num;

den_reg = den;

while (num_reg > 0) {

num reg = num reg - den reg;

i ++;

output = i;

done = 1;

while (go == 1);

```

b. (15 points) For the same pseudo-code, create a datapath capable of executing the code (ignore the controller in this step). Make sure to show all control signals (i.e., mux select signals, register load signals, comparator output signals). Make sure to include a register for *num*, *den*, *output*, and *done* in addition to other registers you might need. To make things easier, I don't recommend sharing resources. **Do not write any code**, **just show the datapath**. If you do any non-obvious optimization, make sure to explain.

c. (15 points) For the datapath in the previous step, draw an FSM capable of controlling the datapath to perform the pseudo-code in part a. In each state of the FSM, show the values of your control signals from the previous step that configure the datapath to do the corresponding operations. Assume that *go* is an input to the controller. Hint: to save time, try to use the same states as the FSMD by changing the operations to the corresponding control signals. **Do not write any VHDL code, just show the FSM and control signals. Be sure to mention default signal values to save space.**

6) **4 free points** for a long test.