| EEL 4712                | Name: | SOLUTION |

|-------------------------|-------|----------|

| Midterm 2 – Spring 2019 |       |          |

| VERSION 1               |       |          |

|                         | UFID: |          |

Sign here to give permission for your test to be returned in class, where others might see your score:

**IMPORTANT:**

• Please be neat and write (or draw) carefully. If we cannot read it with a reasonable effort, it is assumed wrong.

• As always, the best answer gets the most points.

## **COVER SHEET:**

| Problem#:     | Points |

|---------------|--------|

| 1 (12 points) |        |

| 2 (6 points)  |        |

| 3 (6 points)  |        |

| 4 (25 points) |        |

| 5 (25 points) |        |

| 6 (26 points) |        |

Total:

**Regrade Info:**

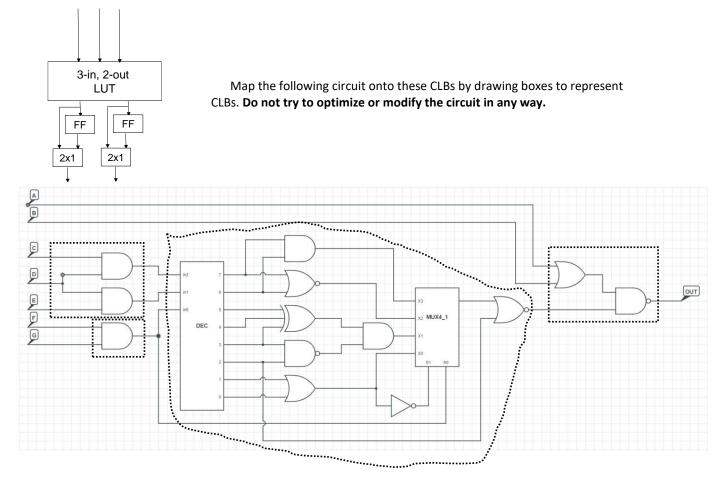

1. (12 points) Assume you are given an FPGA that consists of the following CLB structures with one 3-input, 2-output LUT and optional registers on each output.

2. (6 points) Name three primary FPGA resources, excluding interconnect.

DSPs, LUTs (or CLBs), Block RAM, I/O, PCIe Express, transceivers

3. (6 points) You are designing a circuit that repeatedly outputs a 1-cycle pulse at 6 μs, 11 μs, and 15 μs. Assuming a 50 MHz clock, at what count values should each pulse occur?

One 50 MHz clock period = 1s / 50M = 20 ns.

Clock periods for  $6 \mu s = 6 \mu s / 20 ns = 300$

Clock periods for 11  $\mu$ s = 11  $\mu$ s / 20 ns = **550**

Clock periods for 15  $\mu$ s = 15  $\mu$ s / 20 ns = **750**

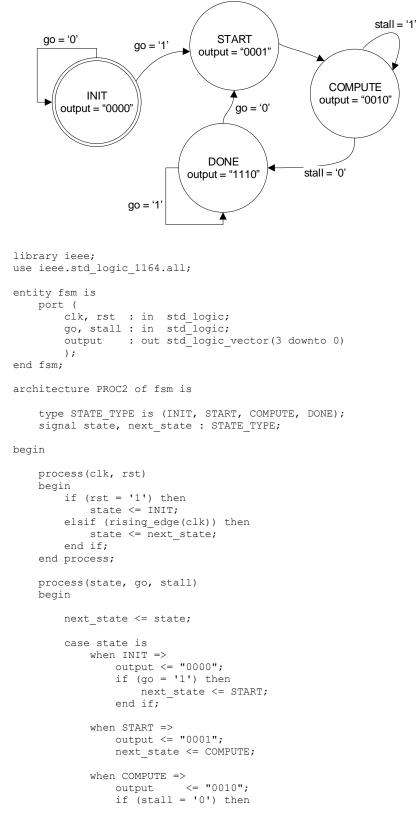

(25 points) Fill in the code to implement the following Moore finite state machine (FSM) using the 2-process FSM model. Assume that INIT is the initial state. Transitions without conditions are always taken. Use the next page if extra room is needed.

```

next_state <= DONE;

end if;

when DONE =>

output <= "1110";

if (go = '0') then

next_state <= START;

end if;

end case;

end process;

```

end PROC2;

5. (25 points) Create an FSMD that implements the following pseudo-code. Do not write VHDL and instead leave the FSMD in graphical form (i.e., state machine with corresponding operations in each state).

```

Inputs: go (std_logic), N (std_logic_vector)

Outputs: result (std_logic_vector), done (std_logic)

// reset values for outputs

done = 0; result = 0;

while (1) {

while (go == 0);

done = 0;

x = 0;

y = 1;

z = 2;

i = 0;

nReg = N; // store input N into a register

while (i < nReg) }

z = 3*y + 5*x;

x = y;

y = z;

i++;

}

result = z;

done = 1;

go = 'O'

while (go == 1);

90='1'

gu<sup>_'u'</sup>

done = 0

x = 0

y = 1

2=2

=0

۱

n Reg = N

; >=nkeg

: <n Reg

result = 2

Z = 3+y +

done =1

x=Y

y=2

'90=<sup>'1'</sup>

++

```

}

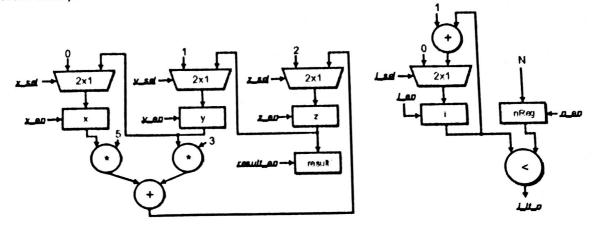

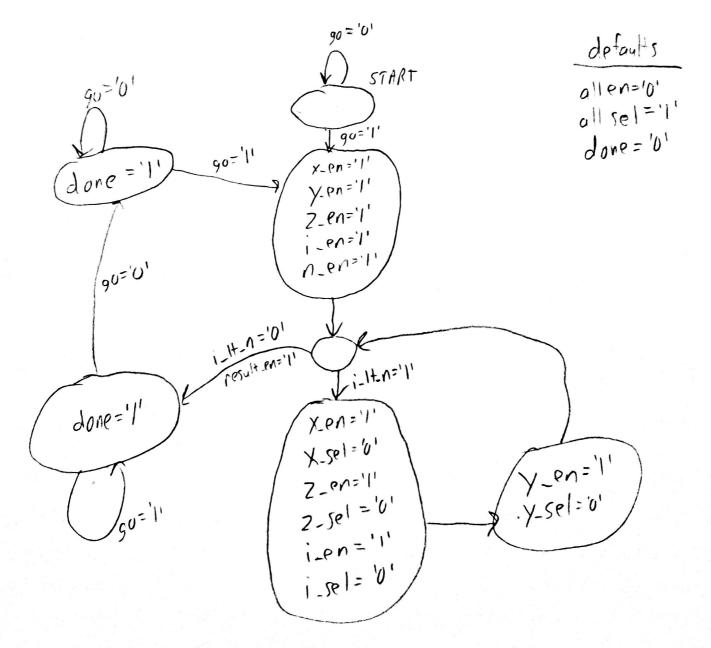

6. (26 points) Draw an FSM capable of controlling the illustrated datapath to perform the pseudo-code in question 5, by assigning or reading from the underlined control signals. The controller should have an additional input for *go* and an output for *done* (not shown in the datapath). Assume that left mux inputs have a select value of 1. *Do not write any VHDL code*, just show the FSM and control signals. Be sure to mention default signal values to save space. NOTE: this FSM might have different states than your FSMD in problem 5.