EEL 4712 – Spring 2015

## Objective:

The objective of this lab is to create a generic-width ALU using behavioral VHDL. When mapped to the board, the ALU will use 4-bit inputs and output, with the output mapped to one 7-segment LED. The data inputs to the ALU are connected to four switches, and the 4-bit select input is connected to 1 switch and 3 buttons. In this lab, you will become familiar with two arithmetic VHDL packages: numeric\_std (recommended) and std\_logic\_arith. In addition, you will get experience using testbenches to verify the correct functionality of the circuits you specify in VHDL.

#### Required tools and parts:

Quartus2 software package, ModelSim-Altera Starter Edition, Altera DE0 board.

## Pre-requisite:

You must be "up-to-speed" with Quartus before coming to lab. Perform Tutorials 1 and 3 (Appendices B and D) in the textbook if necessary. Also, download and read the Altera DE0 documents before coming to lab. You should know how to map the I/O of the top-level VHDL entity onto the corresponding pins on the Altera DE0 board.

### Pre-lab requirements:

1. Design a decoder for the 7-segment display (call it decoder7seg.vhd). The entity must look exactly like this:

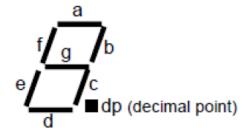

Any changes to this entity will cause the test benches used for grading to fail. Create the VHDL architecture to implement the following functionality. Note that the outputs for the LED segments are active low (i.e. a 0 causes the segment to turn on).

| Input(i3-i0) | Output (a-g) |

|--------------|--------------|

| 0000         | 0000001      |

| 0001         | 1001111      |

| 0010         | 0010010      |

| 0011         | 0000110      |

| 0100         | 1001100      |

| 0101         | 0100100      |

| 0110         | 0100000      |

| 0111         | 0001111      |

| 1000         | 0000000      |

| 1001         | 0001100      |

| 1010         | 0001000      |

| 1011         | 1100000      |

| 1100         | 0110001      |

| 1101         | 1000010      |

| 1110         | 0110000      |

| 1111         | 0111000      |

Figure 1. Voltage Table and diagram for the 7 Segment Display

### Lab 2: Generic-Width Behavioral ALU

EEL 4712 – Spring 2015

Create a VHDL testbench entity (decoder7seg\_tb) for the 7-segment decoder. Save the entity in decoder7seg\_tb.vhd. It is up to you to determine the thoroughness of the testbench. It should test enough cases so you are positive that the architecture is correct. Test your VHDL with the testbench using ModelSim-Altera Starter Edition. See the tutorial linked off the lab website for an explanation on how to use the tool.

**Turn in on e-learning:** decoder7seg.vhd and decoder7seg\_tb.vhd. The TAs will grade your VHDL by running it using a testbench that I am providing. Therefore, *it is critical you do not change the entity declaration*.

2. Create an generic-width ALU using a behavioral architecture with the numeric\_std package. The entity and architecture must appear in a file called alu\_ns.vhd and should have this exact specification:

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity alu_ns is

generic (

WIDTH : positive := 16

);

port (

input1 : in std_logic_vector(WIDTH-1 downto 0);

input2 : in std_logic_vector(WIDTH-1 downto 0);

sel : in std_logic_vector(3 downto 0);

output : out std_logic_vector(WIDTH-1 downto 0);

overflow : out std_logic_

);

end alu_ns;

```

Note that the width of the ALU is defined by a generic. Therefore, you must write the architecture to work for any possible width (i.e., don't assume the input is 16 bits). The operation of the ALU is described below:

| Sel  | Output                                                                                                                                                               | Overflow (assume all operations are unsigned)                                                         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 0000 | input1 + input2                                                                                                                                                      | '1' if input1 + input2 is bigger than the maximum number that can be written to output, '0' otherwise |

| 0001 | input1 - input2                                                                                                                                                      | <b>'0'</b>                                                                                            |

| 0010 | input1*input2 (low half of the mult result. e.g. multiplication of two width-bit numbers results in a width*2-bit number. The output should be the lower width bits) | '1' if input1*input2 is bigger than the maximum number that can be written to output, '0' otherwise   |

| 0011 | Input1 and input2                                                                                                                                                    | <b>'</b> 0'                                                                                           |

| 0100 | Input1 or input2                                                                                                                                                     | '0'                                                                                                   |

| 0101 | Input1 xor input2                                                                                                                                                    | '0'                                                                                                   |

| 0110 | Input1 nor input2                                                                                                                                                    | <b>'</b> 0'                                                                                           |

| 0111 | Not input1                                                                                                                                                           | <b>'</b> 0'                                                                                           |

| 1000 | Shift input1 left by 1 bit                                                                                                                                           | the high bit of input1 before the shift                                                               |

# Lab 2: Generic-Width Behavioral ALU

EEL 4712 – Spring 2015

| 1001 | Shift input1 right by 1 bit                                                                                                                                                                            | '0'         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1010 | Swap the high-half bits of input1 with the low-half bits of input1, write this to output. In the case of an odd width, use 1 extra bit from the high half. For example, 0101000 should become 0000101. | '0'         |

| 1011 | Reverse the bits in input1, write this to output                                                                                                                                                       | <b>'0'</b>  |

| 1100 | 0                                                                                                                                                                                                      | <b>'</b> 0' |

| 1101 | 0                                                                                                                                                                                                      | <b>'</b> 0' |

| 1110 | 0                                                                                                                                                                                                      | <b>'</b> 0' |

| 1111 | 0                                                                                                                                                                                                      | <b>'</b> 0' |

Create a VHDL testbench entity (alu\_ns\_tb). Save the entity in alu\_ns\_tb.vhd. There is small sample testbench on the lab website, but it is up to you to determine the thoroughness of the testbench. It should test enough cases so you are positive that the architecture is correct. Although the entity must be defined using numeric\_std, you can use any package you like for the testbench. Note that the provided example uses std\_logic\_arith to demonstrate different functions.

**Turn in on e-Learning:** alu\_ns.vhd and alu\_ns\_tb.vhd. The TAs will grade your VHDL by running it using a testbench that I am providing. Therefore, *it is critical you do not change the entity declaration.*

3. Design the same generic-width ALU using std\_logic\_arith and std\_logic\_unsigned (instead of numeric\_std). The entity should be saved in alu\_sla.vhd, along with a new testbench in alu\_sla\_tb.vhd. Note that the exact same testbench code can be used. All you have to do is change the name of the alu component that is instantiated. Make sure to use this exact entity specification:

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic arith.all;

use ieee.std logic unsigned.all;

entity alu sla is

generic (

WIDTH : positive := 16

);

port (

input1 : in std logic vector(WIDTH-1 downto 0);

input2 : in std logic vector(WIDTH-1 downto 0);

sel : in std logic vector(3 downto 0);

output : out std logic vector(WIDTH-1 downto 0);

overflow: out std logic

);

end alu sla;

```

**Turn in on e-learning:** alu\_sla.vhd and alu\_sla\_tb.vhd. The TAs will grade your VHDL by running it using a testbench that I am providing. Therefore, *it is critical you do not change the entity declaration.*

### Lab 2: Generic-Width Behavioral ALU

EEL 4712 – Spring 2015

4. Integrate your code with the top\_level structural entity top\_level.vhd (linked off the lab website). Feel free to change the ALU component to use either the numeric\_std or std\_logic\_arith versions. The choice is yours. Make sure you understand which input maps to which switch or button.

**Turn in on e-learning:** A graphical illustration of how the provided VHDL connects the components together. Save the illustration in whatever format is convenient (e.g., pdf, jpeg).

### In-lab procedure:

- 1. Using Quartus, assign pins to each of the top\_level.vhd inputs/outputs such that the signals are connected to the appropriate locations on the board.

- Assign the 4 bits of input1 to the leftmost slide switches on the DE0 board

- Assign the 4 bits of input2 to the next four slide switches on the DE0 board

- Assign 4 bits of the Select input to on the rightmost slide switch (for the highest bit of the select) and the 3 push buttons (for the lower three bits).

- Assign the outputs of the four 7-segment decoders to the four 7-segment LED displays.

- Assign the four decimal point (DP) outputs to the corresponding 7-segment LED displays.

- 2. Download your design to the board, and test it for different inputs and outputs. The TA will ask you to demonstrate at least one example for each possible select.

- Be prepared to answer simple questions or to make simple extensions that your TA may request.

There is no need to memorize the different packages. If you have done the pre-lab exercises, these

questions should not be difficult.

# Lab report: (In-lab part only)

If you had any problems with portions of the lab that could not be resolved during lab, please discuss them along with possible justifications and solutions. If you had no problems, this report is not necessary.

Turn the lab report in on e-learning, if explanation is needed for partial credit. Make sure to turn it in to the "lab" section and not the "pre-lab" section.