| EEL 4712<br>Midterm 3 – Spring 2013<br>VERSION 1                                                                                                                                    |        |  |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--------|

| Sign your name here if you would like for your test to be returned in class:                                                                                                        |        |  |        |

| IMPORTANT:  • Please be neat and write (or draw) carefully. If we cannot read it with a reasonable effort, it is assumed wrong.  • As always, the best answer gets the most points. |        |  |        |

| COVER SHEET:                                                                                                                                                                        |        |  |        |

| Problem#:                                                                                                                                                                           | Points |  |        |

| 1 (14 points)                                                                                                                                                                       |        |  | Total: |

| 2 (7 points)                                                                                                                                                                        |        |  | Total. |

| 3 (7 points)                                                                                                                                                                        |        |  |        |

| 4 (7 points)                                                                                                                                                                        |        |  |        |

| 5 (7 points)                                                                                                                                                                        |        |  |        |

| 6 (7 points)                                                                                                                                                                        |        |  |        |

| 7 (14 points)                                                                                                                                                                       |        |  |        |

| 8 (6 points)                                                                                                                                                                        |        |  |        |

| 9 (6 points)                                                                                                                                                                        |        |  |        |

| 10 (21 points)                                                                                                                                                                      |        |  |        |

| 11 (4 points)                                                                                                                                                                       | 4      |  |        |

| Regrade Info:                                                                                                                                                                       |        |  |        |

|                                                                                                                                                                                     |        |  |        |

|                                                                                                                                                                                     |        |  |        |

|                                                                                                                                                                                     |        |  |        |

|                                                                                                                                                                                     |        |  |        |

```

ENTITY _entity_name IS

PORT(_input_name, __input_name : IN STD_LOGIC;

input vector name: IN STD LOGIC VECTOR( high downto low);

_bidir_name, __bidir_name : INOUT STD_LOGIC;

output name, output name: OUT STD LOGIC);

END entity name;

ARCHITECTURE a OF entity name IS

SIGNAL __signal_name : STD_LOGIC;

BEGIN

-- Process Statement

-- Concurrent Signal Assignment

-- Conditional Signal Assignment

-- Selected Signal Assignment

-- Component Instantiation Statement

END a;

__instance_name: __component_name PORT MAP (__component_port => __connect_port,

component port => connect port);

WITH expression SELECT

_signal <= __expression WHEN __constant_value,

expression WHEN __constant_value,

expression WHEN constant value,

expression WHEN constant value;

_signal <= __expression WHEN __boolean_expression ELSE

expression WHEN boolean expression ELSE

expression;

IF expression THEN

statement;

statement;

ELSIF expression THEN

statement;

statement;

ELSE

__statement;

statement:

END IF;

CASE __expression IS

WHEN __constant_value =>

statement;

statement;

WHEN __constant_value =>

statement;

statement;

WHEN OTHERS =>

statement:

statement;

END CASE;

<generate label>: FOR <loop id> IN <range> GENERATE

-- Concurrent Statement(s)

END GENERATE;

```

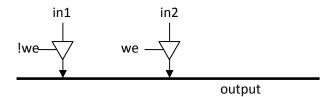

1) a. (7 points) Fill in the following **behavioral** architecture to implement the following bus.

```

library ieee;

use ieee.std logic 1164.all;

entity small_bus is

generic (

positive := 8);

width :

port (

: in std_logic_vector(width-1 downto 0);

in1

in2 : in std_logic_vector(width-1 downto 0);

wen : in std_logic;

output : out std_logic_vector(width-1 downto 0));

end small_bus;

architecture BHV of small_bus is

begin

process(

)

begin

```

```

end process;

end BHV;

```

b. (7 points) Show the synthesized structure when using an FPGA for the code in part a.

2) (7 points) Name two situations where the input to a flip-flop may change during the setup and hold window.

3) (7 points) Show the location in the following circuit where metastability will occur.

4) (7 points) What synchronizer is most effective when trying to maximize bandwidth across clock domains?

5) (7 points) All of the synchronizers discussed in class rely on the dual-flop synchronizer. Are these synchronizers guaranteed to always work? Explain why or why not.

6) (7 points) Identify and describe the problem with the following combinational logic, which commonly occurs when creating 2-process FSMD entities. Note: the problem is not related to synthesis guidelines.

```

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric_std.all;

entity alu is

generic (

width :

positive := 8);

port (

input1 : in std_logic_vector(width-1 downto 0);

input2 : in std_logic_vector(width-1 downto 0);

sel : in std_logic;

output : out std_logic_vector(width-1 downto 0));

end alu;

architecture BHV of alu is

signal feedback : std logic vector(width-1 downto 0);

process(input1, input2, sel, feedback)

begin

if (sel = '1') then

feedback <= std logic vector(unsigned(input1)+unsigned(input2));</pre>

feedback <= std_logic_vector(unsigned(input1)+unsigned(feedback));</pre>

end if;

output <= feedback;

end process;

end BHV;

```

7) (14 points) Create a memory initialization file for the following assembly code. Add a comment to show the beginning of each instruction and each variable in memory. You will likely need to break your answer up into two columns to fit on the page.

```

OUTPORT0

$FFFE

EQU

BEGIN:

VALUE1

LDAA

STAR

VALUE2

LDAA

ANDR

THERE

BEQA

ADCR

D

THERE:

ADCR

D

STAA

OUTPORT0

INFINITE LOOP:

CLRC

INFINITE LOOP

BCCA

* Data Area

VALUE1: dc.b

$55

VALUE2: dc.b

$AA

END

BEGIN

Depth = 256;

Width = 8;

Address radix = hex;

Data radix = hex;

% Program RAM Data %

Content

Begin

```

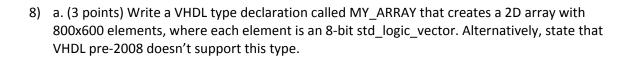

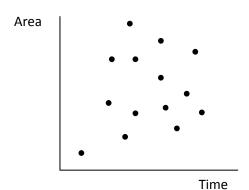

9) a. (3 points) For the set of implementations shown below, circle the implementations that are Pareto optimal. List any assumptions.

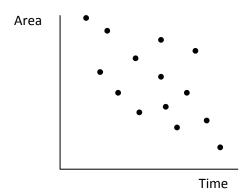

b. (3 points) Do the same for the following set of implementations.

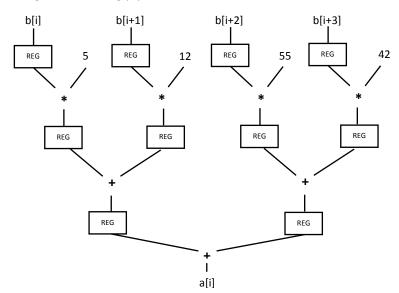

10) a. (7 points) For the following code, create a schedule for the provided datapath. Ignore muxes and other glue logic. Assume that address calculations are done *without* using the specified resources (i.e., address calculations cost nothing). Do not change the code.

```

for (int i=0; i < 1000000; i++) {

a[i] = b[i]*5 + b[i+1]*12 + b[i+2]*55 + b[i+3]*42;

}</pre>

```

## **Datapath**

4 multipliers

3 adders

1 memory for b[] (can read 4 elements/cycle)

1 memory for a[] (can write 1 element/cycle)

- b. (7 points) Show the execution time in total cycles based on your schedule from part a.

- c. (7 points) Estimate the total cycles when using the following pipeline:

11) (4 free points) Write or draw something funny if you have time left.