| EEL 4712              |                      | Name:                                         |                               |   |

|-----------------------|----------------------|-----------------------------------------------|-------------------------------|---|

| Midterm 2 – Spring    | 2013                 |                                               |                               |   |

| VERSION 1             |                      |                                               |                               |   |

|                       |                      | UFID:                                         |                               | _ |

| Sign vour name here   | e if you would like  | e for your test to be re                      | turned in class:              |   |

| Sign your marrie here | ; ii you would like  | s for your test to be re                      | turrieu iii ciass.            |   |

|                       |                      |                                               |                               |   |

|                       |                      |                                               | _                             |   |

|                       |                      |                                               |                               |   |

| IMPORT                |                      |                                               |                               |   |

|                       |                      |                                               | . If we cannot read it with a |   |

|                       | ole effort, it is as | ssumed wrong.<br>I <b>nswer gets the mo</b> s | et nointe                     |   |

| - As alw              | ays, the best a      | mswer gets the mos                            | st points.                    |   |

|                       |                      |                                               |                               |   |

| <b>COVER SHEE</b>     | ET:                  |                                               |                               |   |

|                       |                      | -                                             |                               |   |

| Problem#:             | Points               |                                               |                               |   |

| 1 (18 points)         |                      |                                               |                               |   |

| 2 (10+                |                      | -                                             | Total:                        |   |

| 5 extra credit)       |                      |                                               |                               |   |

| 3 (12 points)         |                      | ]                                             |                               |   |

| 4 (6 points)          |                      |                                               |                               |   |

| 5 (6 points)          |                      | -                                             |                               |   |

| 6a (16 points)        |                      | -                                             |                               |   |

| 6b (16 points)        |                      | -                                             |                               |   |

| 6c (16 points)        |                      | -                                             |                               |   |

|                       |                      | ]                                             |                               |   |

| Regrade Info:         |                      |                                               |                               |   |

| Regiaue IIIIo.        |                      |                                               |                               |   |

|                       |                      |                                               |                               |   |

|                       |                      |                                               |                               |   |

|                       |                      |                                               |                               |   |

|                       |                      |                                               |                               |   |

|                       |                      |                                               |                               |   |

|                       |                      |                                               |                               |   |

|                       |                      |                                               |                               |   |

|                       |                      |                                               |                               |   |

|                       |                      |                                               |                               |   |

```

ENTITY _entity_name IS

PORT( input name, input name: IN STD LOGIC;

input vector name: IN STD LOGIC VECTOR( high downto low);

_bidir_name, __bidir_name : INOUT STD_LOGIC;

output name, output name: OUT STD LOGIC);

END entity name;

ARCHITECTURE a OF entity name IS

SIGNAL __signal_name : STD_LOGIC;

BEGIN

-- Process Statement

-- Concurrent Signal Assignment

-- Conditional Signal Assignment

-- Selected Signal Assignment

-- Component Instantiation Statement

END a;

__instance_name: __component_name PORT MAP (__component_port => __connect_port,

component port => connect port);

WITH expression SELECT

_signal <= __expression WHEN __constant_value,

expression WHEN __constant_value,

_expression WHEN __constant_value,

_expression WHEN __constant_value;

signal <= __expression WHEN __boolean_expression ELSE

expression WHEN __boolean_expression ELSE

expression;

IF expression THEN

statement;

statement;

ELSIF expression THEN

_statement;

statement;

ELSE

__statement;

statement:

END IF;

CASE __expression IS

WHEN __constant_value =>

statement;

statement;

WHEN __constant_value =>

statement;

statement;

WHEN OTHERS =>

statement;

statement;

END CASE;

<generate label>: FOR <loop id> IN <range> GENERATE

-- Concurrent Statement(s)

END GENERATE;

type __identifier is type_definition;

subtype identifier is subtype indication;

```

| 1) | a. (6 points) For a VGA resolution of 800x600 and a pixel clock of 40 MHz, the h_sync pulse takes 3.2 us. Assuming you have a counter that starts counting at the beginning of the h_sync pulse, what count should represent the end of the h_sync pulse? Show your work.                                             |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | b. (6 points) The Cyclone III EP3C16 has 56 M9k block RAMs, which each contain 9,000 bits. Show whether or not it is possible to store a 640x480 12-bit image in the available block RAM. Assume the individual block RAMs can be combined to form larger memories. No points will be given unless the work is shown. |

|    | c. (6 points) The ROM used in lab6 had a 1-cycle read latency. Consider a situation where the image is stored in off-chip SRAM that has a read latency of 20 cycles. Explain how the rest of the VGA circuit should be modified to account for this increased latency.                                                |

2) (15 points) Identify the violations of the *synthesis coding guidelines* in the following 2-process FSM. Be sure to explain the violation and state if the violation is related to sequential or combinational logic. See the comments for the purpose of each region of code.

```

architecture PROC2 of FSM is

type STATE_TYPE is (STATE_0, STATE_1, STATE_2);

signal state, next_state : STATE_TYPE;

begin

-- state register

process(clk, rst)

begin

if (stall = '0') then

if (rst = '1') then

state <= STATE 0;

elsif(clk'event \overline{a}nd clk = '1') then

state <= next_state;

end if;

end if;

end process;

-- next-state combinational logic

process (en)

begin

case state is

when STATE 0 =>

output <= "001";

if (en = '1') then

next state <= STATE 1;

end if;

when STATE 1 =>

output <= "010";

if (en = '1') then

next_state <= STATE_2;</pre>

end if;

when STATE 2 =>

output <= "100";

if (en = '1') then

next state <= STATE 0;

end if;

when others => null;

end case;

end process;

end PROC2;

```

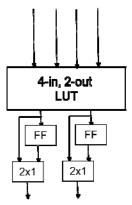

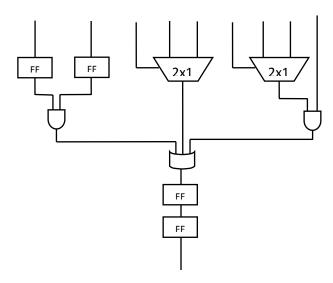

3) (12 points) Assume you are given an FPGA that consists of the following CLB structures:

Map the following circuit onto these CLBs by drawing rectangles to represent CLBs. Use the minimum number of CLBs.

4) (6 points) Show the sequence of FPGA resources that establish a connection between two CLBs that are placed far apart on the FPGA.

5) (6 points) Name two resources other than CLBs that commercial FPGAs include in the fabric. Do not list routing resources.

6) a. (16 points) Create an FSMD that implements the following pseudo-code. **Do not write VHDL** and instead leave the FSMD in graphical form (i.e., state machine with corresponding operations in each state). Make sure to specify all operations and state transitions. Note that input, output, go, and done are I/O.

```

Inputs: go, input

Outputs: output, done

done = 0;  // reset values for outputs

output = 0; // reset values for outputs

while (1) {

while (go == 0);

done = 0;

input_reg = input; // Store input in a register.

i = 0;

do {

sqr = i*i;

i ++;

while (sqr < input_reg);</pre>

output = i-1;

done = 1;

while (go == 1);

```

b. (16 points) For the same pseudo-code, create a datapath capable of executing the code (ignore the controller in this step). Make sure to show all control signals (i.e., mux select signals, register load signals, comparator output signals). Make sure to include a register for *input*, *output*, and *done* in addition to other registers you might need. To make things easier, I don't recommend sharing resources. **Do not write any code**, **just show the datapath**. If you do any non-obvious optimization, make sure to explain.

c. (16 points) For the datapath in the previous step, draw an FSM capable of controlling the datapath to perform the pseudo-code. In each state of the FSM, show the values of your control signals from the previous step that configure the datapath to do the corresponding operations. Hint: to save yourself time, try to use the same states as the FSMD, and just change the operations to the corresponding control signals. Do not write any VHDL code, just show the FSM and control signals. Be sure to mention default signal values to save space.