### Introduction:

In this lab, you will be implementing and testing some basic digital circuits in VHDL to familiarize yourself with VHDL simulations and synthesis. Before starting, download all provided code off the website, which includes skeleton VHDL files and testbenches for simulations. If you are confused about the how each entity works, use google or look at the testbench code to see the correct output. Make sure to read my provided VHDL tutorial. Instructions for how to simulate and synthesis will be given in class, although I encourage you to figure it out from the ISE documentation.

You will submit this lab on e-learning, but it will not be graded. Instead, in the case of borderline final grades, I will check to see how much effort was made on this lab. When submitting the lab, include all vhd files in addition to screenshots of working simulation waveforms.

## Part 1 – Install Xilinx ISE

See the link on the lab website. You can install the latest version if you want, but be aware that later on in the semester, you will be working with code that only works with versions 10.1 and earlier. So, at the very least, install 10.1. If you want a newer version, install both. Some of the previous versions had problems with 64-bit operating systems, but I think that was solved with 10. If you can't get version 10 to work, let me know and I'll find another solution.

## Part 2 – ISE Tutorial

Read the ISE tutorials linked off the lab website. Note that the detailed tutorial is very long. You do not need to go through the entire tutorial. As long as you are reasonably comfortable with the features of ISE, you will be fine. I will be demonstrating much of the functionality during class.

## Part 3 – VHDL Tutorial

For all of the following parts, complete the specified entity and the simulate using the testbench with the same name and a \_tb suffix. Ensure there are no failed assertions. Then, synthesize the entity in Xilinx ISE (for any FPGA) and ensure that there are no warnings.

## 3.1 – 2-to-4 Decoder

Modify the dec2to4.vhd file to implement a 2-to-4 decoder using 4 different architectures. Implement each architecture using the construct suggested by the architecture name (e.g., with select, when else, if, case).

## 3. 2 – 4-to-2 Priority Encoder

Create a 4-to-2 priority encoder (enc4to2.vhd). For this part, you only need two architectures based on the if and the case statement. Assume that higher inputs have priority over lower inputs. The valid output should be asserted when any of the inputs are 1 and should be 0 when all the inputs are 0. This valid bit is needed to understand the output of "00" for an input of "0001" and for an input of "0000".

## 3.3 – Adder + Register

Create an adder followed by a register (add\_pipe.vhd). As specified in the provided file, you should use a behavioral implementation. Note that the output of the adder is one bit wider than the inputs. In other words, the output should include the carry. Although it shouldn't matter, you can assume the inputs are unsigned.

# 3.4 – Multiplier + Register

Repeat part 3.3, but replace the adder with a multiplier (mult\_pipe.vhd). The output of the multiplier should be twice the width of the inputs.

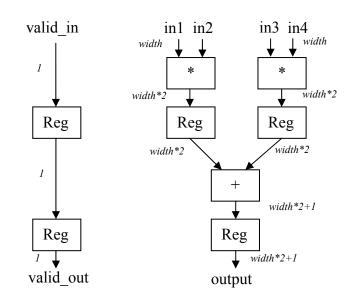

# 3.5 – Datapath

Implement the following datapath structurally. Use the entities from part 3.3 and part 4.3 where applicable, along with the provided register entity (reg.vhd) for the valid output logic on the left.

I